2025 年,Google 最新一代 TPU Trillium 的芯片布局设计室里,没有工程师熬夜调整宏单元位置——完成这项工作的是一个名为 AlphaChip 的强化学习智能体。这场景听着像科幻,但已经发生了。行业还在讨论”AI 能否写好 Verilog”时,一场更深层的转变已经在发生:EDA(电子设计自动化)正从L2 级的”AI 辅助”迈向L3 级的”Agentic EDA”。

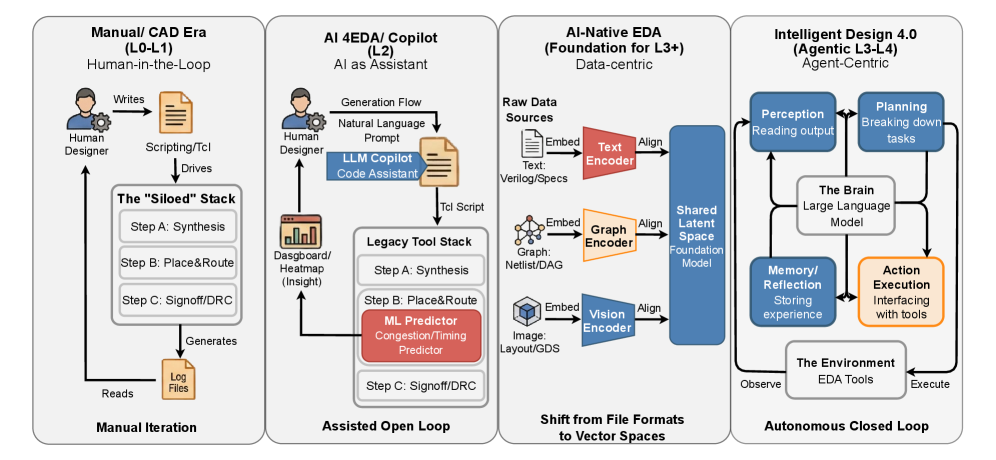

这不是工具升级那么简单,而是”谁在驾驶”的问题。L2 时代,人类定义流程,AI 预测结果;L3 时代,AI 驱动任务,人类负责监控。最新论文《The Dawn of Agentic EDA: A Survey of Autonomous Digital Chip Design》把这一转变定义为”约束神经符号优化问题”——概率性的智能体必须在零容错的物理定律中导航。

问题很尖锐:当 LLM 驱动的自主智能体还没展示完整的、无人工干预的工业级芯片 tape-out 时,我们距离真正的 Agentic EDA 还有多远?

生产力缺口倒逼范式转变

半导体行业面临一个残酷的数学题:

设计复杂度的增长是指数级的,而人类设计能力的增长是线性的。

SoC 设计中的晶体管数量已超过数千亿,但设计团队规模没法同比例扩张。这一”生产力缺口”在历史上曾通过抽象浪潮应对——从手工布局到算法自动化,再到 ML 预测。但现在,缺口正在撕裂。

数据摆在那里:

• 全球 EDA 市场规模 2025 年约125 亿美元,2024-2028 年预计增长87 亿美元(Technavio)

• 验证环节占整个设计周期的60% 以上

• GPT-4o 在 VerilogEval 基准测试上的通过率约63%——但这只是模块级语法测试,用纸飞机评判飞机工程师

三大 EDA 巨头(Synopsys、Cadence、Siemens EDA)占据全球约 78% 的市场份额,它们的动作代表了行业风向:

•Synopsys于 2025 年 9 月宣布扩展 Synopsys.ai™ Copilot 的生成式 AI 能力

•Cadence通过收购 ChipStack 推出全球首个自动化芯片设计和验证的”Super Agent”工作流

•Siemens EDA在 2025 年 DAC 会议上发布 Aprisa AI,覆盖 RTL→GDS 完整工作流

这些动作说明一件事:Agentic AI 不再是学术玩具,而是生产力工具。

Agentic EDA 不是”Chat with Tools”

行业内外对 Agentic EDA 有个普遍误解:以为它只是”用自然语言和 EDA 工具对话”。这种理解严重低估了技术难度。

论文提出了一个关键区分:

Agentic EDA 是一个约束神经符号优化问题,而不是简单的对话界面。

认知栈三层架构

真正的 Agentic EDA 需要跨越三层认知栈:

1. 感知层(Perception):多模态语义对齐

智能体需要”看懂”时序图、拥塞图、日志文件,并将这些异构信息对齐为统一的语义表示。这远不止是读取文本日志。

2. 认知层(Cognition):严格约束下的规划

在功耗、性能、面积(PPA)的多目标优化中,设计空间巨大且非凸。智能体必须在物理定律的硬约束下进行推理,而不是自由发挥。

3. 行动层(Action):确定性工具执行

生成的 Tcl 脚本、RTL 代码必须被 EDA 工具精确执行,任何语法错误都会导致流程中断。

双环修复机制

前沿系统采用双环修复机制来应对这一挑战:

•快速语法环:编译器日志过滤语法错误,分钟级修复

•慢速语义环:通过仿真波形或抽象语法树(AST)追踪功能因果,小时级调试

这种机制承认了一个事实:LLM 可以生成语法正确的代码,但无法保证功能正确。

语义盲点——模型生成语法正确但功能无用的 Verilog(如时序违规)——是当前技术的核心瓶颈。

这类问题正是 AI+EDA 可以发力的地方。智能日志分析能把 Bug 定位效率提升 200%;代码辅助生成能减少重复性劳动。智语芯就是做这个的工具,已经在实际芯片设计流程里验证过。

从”画布”到”代码”的演进

布局布线(Place & Route)领域的技术演进很有代表性。早期方法将布局视为图像生成问题(CNN 预测宏单元位置),但像素表示与 EDA 约束不匹配。现在前沿已经转向:

•强化学习(AlphaChip、MaskPlace):序列决策,PPA 质量高但迁移性差

•扩散模型(DiffusionPlace):条件去噪任务,零样本泛化能力强

•图神经网络(TransPlace):电路拓扑嵌入,兼顾速度与质量

•智能体编排(CodeNotCanvas、ChatEDA):多智能体协作,脚本生成成功率达 98.3%

ChatEDA 的 98.3% 成功率常被引用,但关键问题是:这 1.7% 的失败案例是否包含致命错误?工业级 tape-out 不允许”差不多”。

人才缺口的双刃剑

Forbes 在 2025 年的一篇文章里提过一个观点:

“通过整合 Agentic AI 到设计和制造工作流,组织可以削弱劳动力短缺并将其转化为优势。”

这话听着像企业宣传,但背后有真实痛点。中国 EDA 行业长期面临人才缺口——培养一个能独立负责后端签核的工程师需要 5-8 年,而行业扩张速度远超人才供给。

Agentic AI 的价值在这里:

•短期(1-2 年):L3 智能体当”强大副驾”,自动化脚本生成(Tcl)、日志分析、重复性调试

•中期(3-5 年):前提是 Sim-to-Real 基准测试弥合差距,智能体可自主负责块级流程

•长期(5+ 年):全芯片智能体架构探索,需要认证保证

但这里有个经济账:智能体推理成本(比如用 GPT-4o 每次调试会话 30 美元)vs 人类劳动力。单纯比较 hourly rate 是误导——

智能体的价值不在于比实习生便宜,而在于比疲惫的工程师更快。错过 tape-out 窗口的成本是数百万美元,而智能体可以 24/7 工作。

硅验证求解器 vs 智能体原型

必须做一个关键区分:

硅验证求解器:如 AlphaChip 已成功实现工业 tape-out,应用于 Google 最近三代 TPU(包括最新 Trillium 第 6 代)。这是强化学习优化宏单元放置的成功案例,有真实芯片背书。

智能体原型:目前没有 LLM 驱动的自主智能体展示完整的、无人工干预的工业芯片 tape-out。大多数学术智能体优化代理指标(如布局线长),使用开源 PDK(如 Sky130),不反映先进节点(如 TSMC N3)的复杂物理效应。这一Sim-to-Silicon 缺口

是行业必须正视的挑战。用论文的原话:”当前 LLM 驱动的自主智能体尚未展示完整的、无人工干预的工业级芯片 tape-out。”

从信任模型到信任证明Agentic EDA 大规模部署的最大障碍不是技术,而是信任。

传统 EDA 算法(如 A*搜索)是确定性的、数学有界的。LLM 驱动的智能体是概率性的、不透明的。这种根本差异导致四类风险:

•模型完整性:硬件木马插入 → 意图分析、异常检测、代码清理

•幻觉:协议违规、无效语法 → 结构化思维链、形式验证反馈

•基础设施:受损 DRC 规则集 → 可审计生成、确定性检查器

•数据隐私:训练数据泄露 → 联邦学习、本地部署、差分隐私

范式转变:信任工程

应对策略不是”让人类在环监督”,而是

信任工程

的范式转变:

•可追溯性:智能体必须提供推理轨迹(思维链),将高级意图与低级行动联系起来

•证明携带代码:智能体应输出 RTL 及伴随的形式化属性(SVA),证明生成的代码符合规范

•从信任模型转向信任证明:模型会错,但机械可验证的证明不会

这需要标准化接口协议——类比软件工程中的语言服务器协议(LSP),将 EDA 工具状态(时序图、拥塞图)暴露为结构化、机器可读的 API。开放 Agentic EDA 标准是行业基础设施的迫切需求。

递归自我改进的愿景

长期来看,最激进的愿景是

AI 设计 AI 硬件的递归循环:智能体优化新架构,协助设计下一代训练更强智能体的芯片。这听着像技术奇点叙事,但约束神经符号规划可能为其他物理工程领域(如机械 CAD、建筑 BIM)提供蓝图。

写在最后

回到开篇的问题:我们距离真正的 Agentic EDA 还有多远?

答案是谨慎乐观。AlphaChip 的成功证明 AI 可以在特定子任务上超越人类,但完整 RTL-to-GDSII 流程的自主编排仍面临 Sim-to-Silicon 缺口、信任赤字、经济可行性三重挑战。

务实的路线图已经清晰:

•2026-2027 年:L3 智能体当标准副驾,覆盖脚本生成、日志分析、重复性调试

•2028-2030 年:块级流程自主化,前提是系统级基准测试(如 RTLLM)弥合学术与工业差距

•2030 年以后:全芯片智能体架构探索,需要形式化认证保证

对于中国 EDA 行业,这既是挑战也是机会。三大巨头占据 78% 市场份额的格局在 AI 时代可能被重构——前提是我们在开放标准、基准测试、人才培养上做出正确选择。

Agentic EDA 的黎明已经到来,但日出还需要时间。在这场范式革命中,最危险的不是技术不成熟,而是过早的过度承诺或过晚的犹豫不决。

在零容错的物理定律面前,务实比激情更有价值。

转自作者:麒芯基于论文《The Dawn of Agentic EDA: A Survey of Autonomous Digital Chip Design》(arXiv:2512.23189)及行业公开资料撰写。

评论(0)