在上一篇文章,我们通过执行Cadence SKILL脚本,在virtuoso的版图里绘制一个通孔阵列。

如果每次想要创建图形的时候都要运行一次脚本,其实还挺麻烦的,而且图形的长宽、间距、位置等参数都要在代码里修改,不够方便。有没有更自动化的方法?有的,答案是创建Pcell。

Pcell即参数化单元,它是一种可编程单元,允许用户在创建单元的时候自定义参数。PDK里的晶体管、电容、电感等元件,就是Pcell。

我们使用Cadence SKILL脚本可以创建一个Pcell。创建完成后,就可以调用该Pcell,并随时自定义其参数,而无需再运行脚本了,自动化程度更上一层楼。

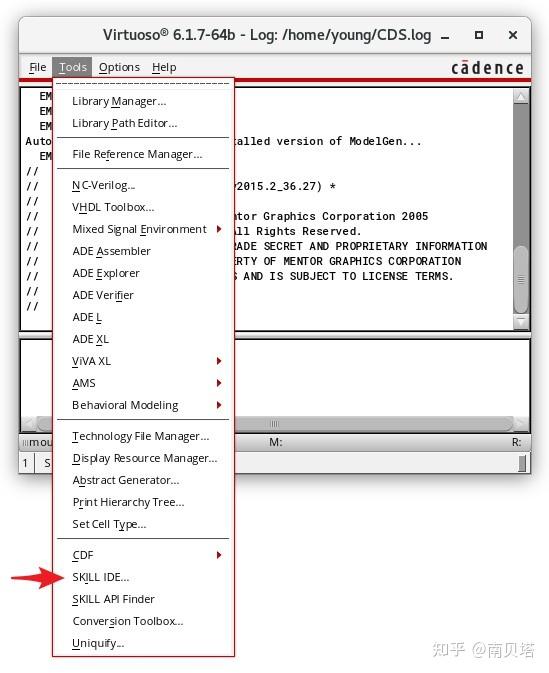

首先仍然是在CIW窗口里点击「Tools > SKILL IDE」,启动SKILL脚本的IDE。

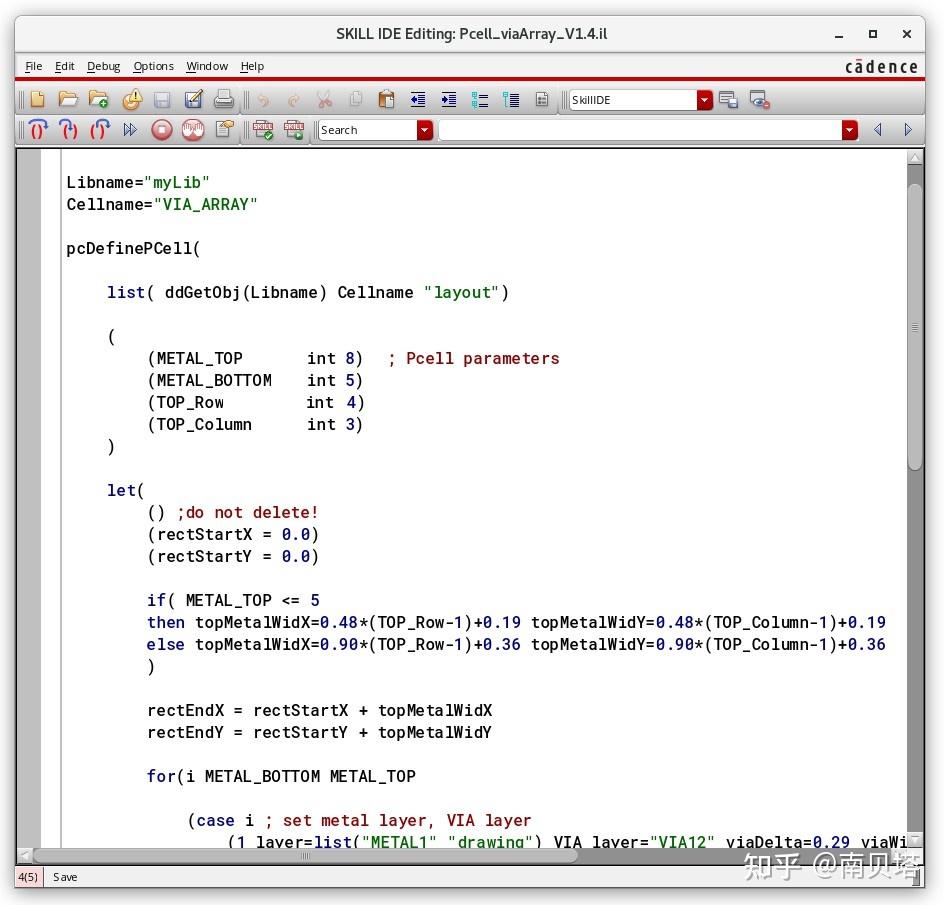

在IDE里,我们编辑SKILL脚本来实现创建Pcell,此处的代码的功能是创建一个通孔阵列的Pcell,其所用的金属层、通孔阵列的行数和列数都可以由用户定义,通孔的间距则根据PDK的DRC规则所允许的最小间距自动计算。

Libname="myLib"

Cellname="VIA_ARRAY"

pcDefinePCell(

list( ddGetObj(Libname) Cellname "layout")

(

(METAL_TOP int 8) ; Pcell parameters

(METAL_BOTTOM int 5)

(TOP_Row int 4)

(TOP_Column int 3)

)

let(

() ;do not delete!

(rectStartX = 0.0)

(rectStartY = 0.0)

if( METAL_TOP <= 5

then topMetalWidX=0.48*(TOP_Row-1)+0.19 topMetalWidY=0.48*(TOP_Column-1)+0.19 ; width of the top metal.

else topMetalWidX=0.90*(TOP_Row-1)+0.36 topMetalWidY=0.90*(TOP_Column-1)+0.36

)

rectEndX = rectStartX + topMetalWidX

rectEndY = rectStartY + topMetalWidY

for(i METAL_BOTTOM METAL_TOP

(case i ; set metal layer, VIA layer

(1 layer=list("METAL1" "drawing") VIA_layer="VIA12" viaDelta=0.29 viaWid=0.19)

(2 layer=list("METAL2" "drawing") VIA_layer="VIA23" viaDelta=0.29 viaWid=0.19)

(3 layer=list("METAL3" "drawing") VIA_layer="VIA34" viaDelta=0.29 viaWid=0.19)

(4 layer=list("METAL4" "drawing") VIA_layer="VIA45" viaDelta=0.29 viaWid=0.19)

(5 layer=list("METAL5" "drawing") VIA_layer="VIA56" viaDelta=0.29 viaWid=0.19)

(6 layer=list("METAL6" "drawing") VIA_layer="VIA67" viaDelta=0.54 viaWid=0.36)

(7 layer=list("METAL7" "drawing") VIA_layer="VIA78" viaDelta=0.54 viaWid=0.36)

(8 layer=list("METAL8" "drawing") VIA_layer="VIA89" viaDelta=0.54 viaWid=0.36)

)

viaRowNum = int((topMetalWidX-viaWid)/(viaWid+viaDelta))+1

viaStartX = (topMetalWidX-(viaRowNum-1)*(viaWid+viaDelta)-viaWid)/2

viaColNum = int((topMetalWidY-viaWid)/(viaWid+viaDelta))+1

viaStartY = (topMetalWidY-(viaColNum-1)*(viaWid+viaDelta)-viaWid)/2

rodCreateRect(

?layer layer

?width topMetalWidX

?length topMetalWidY

?origin list( rectStartX rectStartY )

)

if( i != METAL_TOP ; create via layer. Do not create if it is top metal.

then

rodCreateRect(

?layer VIA_layer

?width viaWid

?length viaWid

?origin list( viaStartX viaStartY )

?elementsX viaRowNum

?elementsY viaColNum

?spaceX viaDelta

?spaceY viaDelta

)

)

)

)

)

来看看创建Pcell的SKILL代码,把细节的代码略去,其框架如下:

Libname="myLib"

Cellname="VIA_ARRAY"

pcDefinePCell(

list( ddGetObj(Libname) Cellname "layout")

(

; Pcell parameters

)

let(

; code here

)

)

首先定义想要放置Pcell的Library名称「myLib」,以及Pcell的名称「VIA_ARRAY」。

接下来调用「pcDefinePCell」函数,函数里第一行代码传入我们所定义的Pcell的library名称、Pcell名称以及Pcell的cellview类型,此处指定其类型是版图「layout」。

在接下来的一对括号里,定义Pcell供用户自定义的参数,此处指定了通孔阵列的顶层金属层、底层金属层、行数、列数。

在接下来的「let」里,就可以开始编写代码实现Pcell的功能了,此处我们绘制了通孔阵列的版图图案。

以上就是创建Pcell的SKILL脚本的框架。

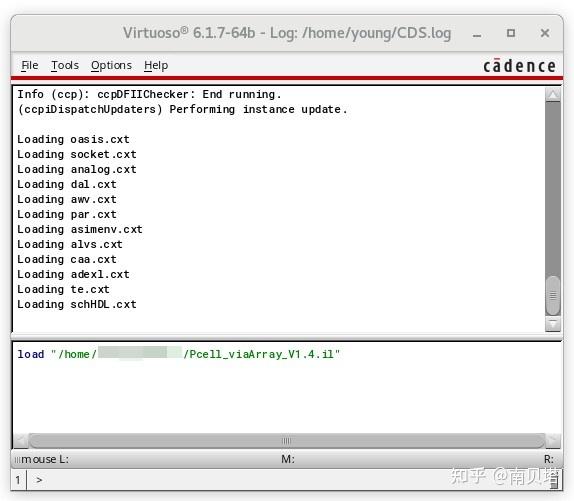

编写完脚本后保存至本地,然后在CIW窗口的命令行中load这个脚本:

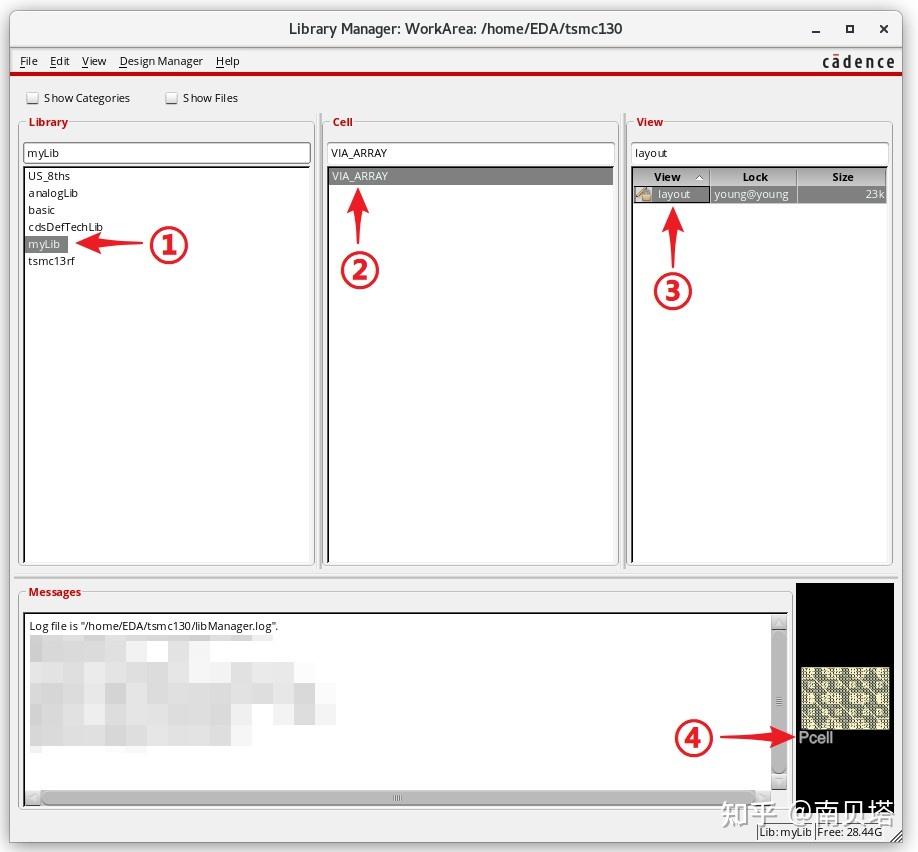

脚本顺利执行后,我们打开Library Manager,可以看到在库「myLib」里出现了一个叫「VIA_ARRAY」的cell,他的类型是「layout」,查看右下角缩略图,可以看到「Pcell」的标记。这些信息都与我们上面定义的相符。

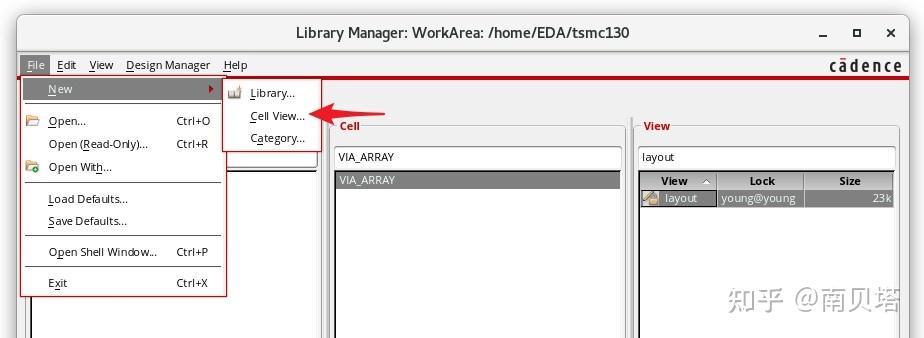

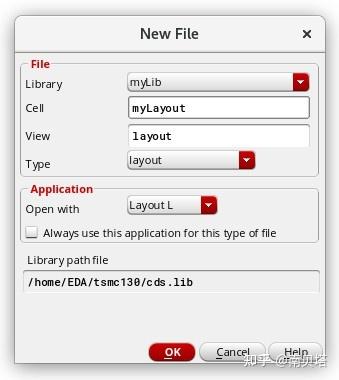

现在来尝试使用这个Pcell。在library manager点击「File > New > Cell View」,新建一个layout。

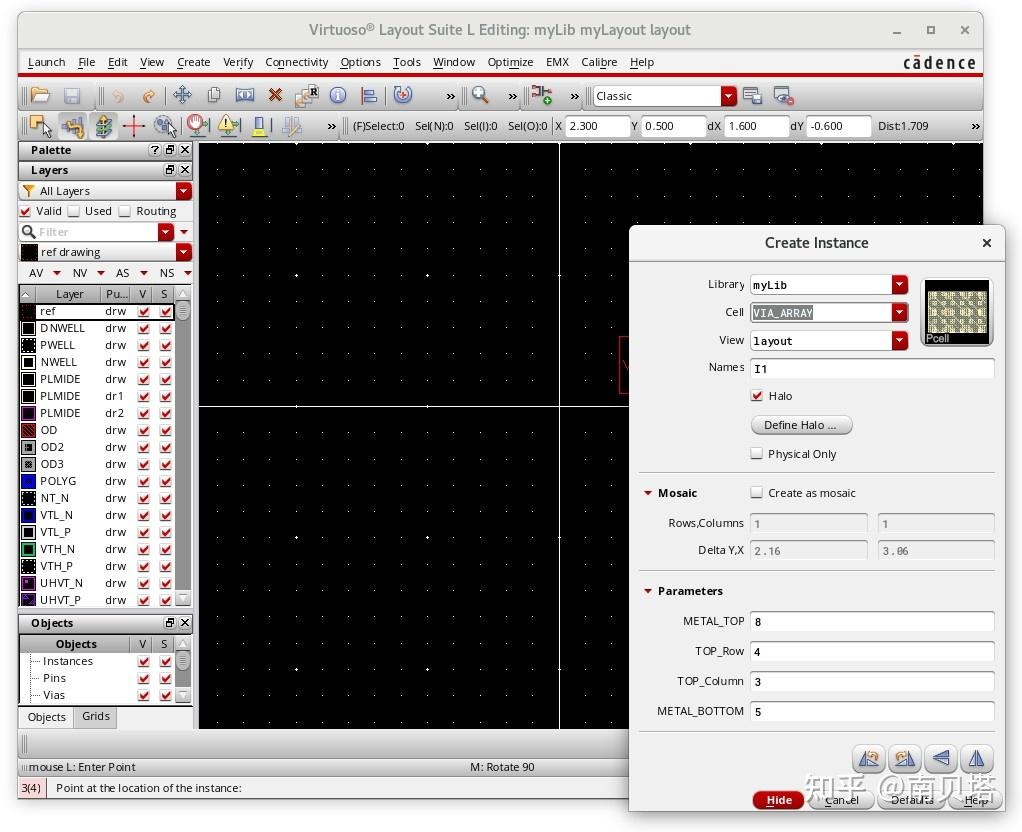

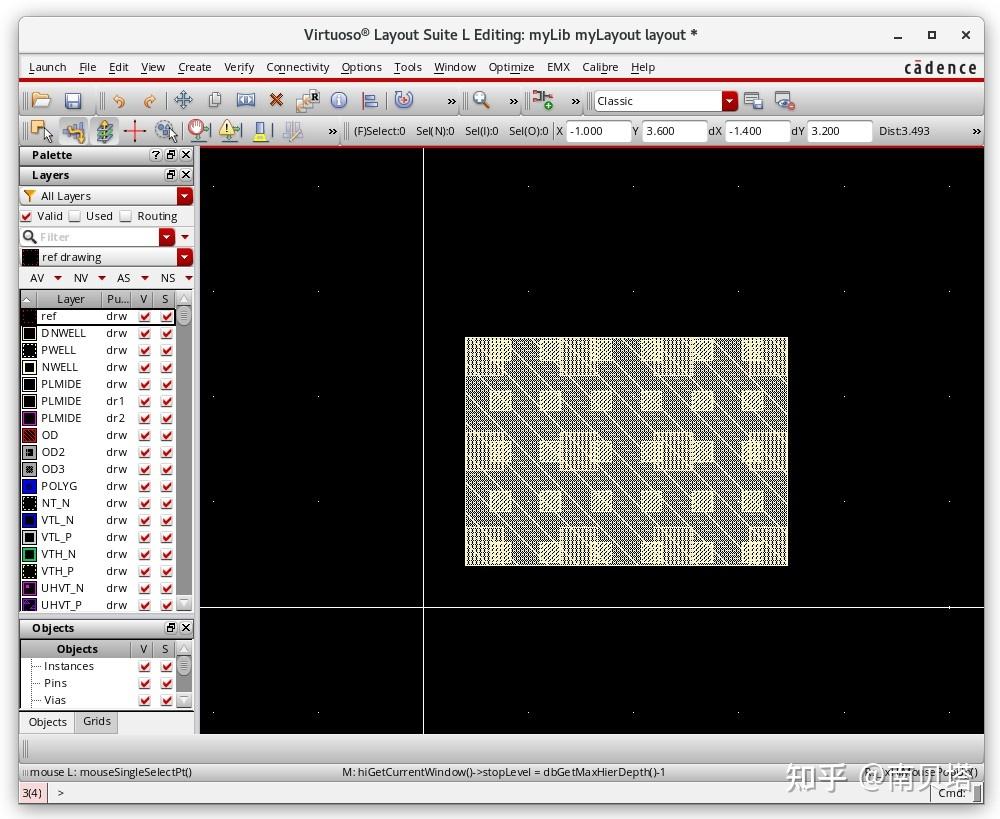

在新建的layout里,点击「i」插入元件,选择我们所创建的位于「myLib」的「VIA_ARRAY」Pcell,可以看到,我们可以自定义通孔阵列的顶层金属层、底层金属层、行数、列数。这与我们上面定义的相符。定义后插入,顺利在layout中放置了一个通孔阵列。这个通孔阵列的参数随时可以修改,其坐标也可以拖动。

评论(0)